# **NVIDIA Jetson Xavier NX Series System**on-Module

Volta GPU + Carmel CPU + LPDDR4x + 16GB eMMC 5.1

**Data Sheet**

# **Document History**

### DS-10184-001-v1.9

| Version            | Date              | Description of Change                                                                                 |

|--------------------|-------------------|-------------------------------------------------------------------------------------------------------|

| v1.0               | November 6, 2019  | Initial release.                                                                                      |

| v1.1               | February 1, 2020  | Updated:                                                                                              |

|                    |                   | > PCIEO_XXX pins from Ctrl #0 to Ctrl #5 under PCle Pin description in Table 9: PCle Pin Descriptions |

|                    |                   | > PCIE1_XXX pins from Ctrl #1 to Ctrl #4 under PCle Pin description in Table 9: PCle Pin Descriptions |

|                    |                   | > Pulse Width Modulator (PWM) to reflect four outputs instead of eight outputs                        |

|                    |                   | > SHUTDOWN_REQ* and SYS_RESET* pull up information in Table 21:<br>Power and System Control Pins      |

|                    |                   | > Absolute Maximum Ratings to include the Mounting Force parameter.                                   |

|                    |                   | > Mechanical Drawing                                                                                  |

| v1.2               | February 24, 2020 | Added:                                                                                                |

|                    |                   | > Tolerance information for Mechanical Drawing                                                        |

| v1.3               | April 21, 2020    | Added:                                                                                                |

|                    |                   | > PMIC_BBAT to reflect RTC accuracy                                                                   |

|                    |                   | > SoC height for the Mechanical Drawing                                                               |

|                    |                   | > Table 30: Jetson NX Reliability Report table                                                        |

|                    |                   | > Gen4 information to PCI Express (PCIe) section                                                      |

| v1.4 June 25, 2020 |                   | Added:                                                                                                |

|                    |                   | > Programmable Vision Accelerator (PVA) section to Functional Overview Updated:                       |

|                    |                   | > Table 6: Video Decoder Standards table                                                              |

| v1.5 July 06, 2020 |                   | Added:                                                                                                |

|                    | ,                 | > Overcurrent Throttling section to Power and System Management                                       |

| v1.6               | October 23, 2020  | Updated:                                                                                              |

|                    |                   | > SHUTDOWN_REQ* pin changed from Input to Output                                                      |

|                    |                   | > Document number of data sheet                                                                       |

|                    |                   | Added:                                                                                                |

|                    |                   | > SPI Slave Timing Parameters and Diagram                                                             |

| v1.7               | July 29, 2021     | Updated:                                                                                              |

|                    |                   | > Video Decoder Standards Table                                                                       |

|                    |                   | > Video Encoder Standards Table                                                                       |

|                    |                   | > 20W information for GPU Operation, CPU Operation, DLA Clock, and PVA clock tables                   |

|                    |                   | > Maximum DRAM frequency from 1600 to 1866                                                            |

| v1.8               | December 14, 2021 | Added:                                                                                                |

|                    |                   | > Added support for Jetson Xavier NX 16GB                                                             |

|                    |                   | Updated:                                                                                              |

|                    |                   | > Memory section: added LPDDR4x Memory Bus table                                                      |

| Version | Date            | Description of Change           |  |

|---------|-----------------|---------------------------------|--|

| v1.9    | January 8, 2024 | Updated:                        |  |

|         |                 | > Overcurrent Throttling        |  |

|         |                 | > PMIC_BBAT section             |  |

|         |                 | > CUDA 10 to CUDA 11.4+         |  |

|         |                 | Added:                          |  |

|         |                 | > Environmental Testing table   |  |

|         |                 | > Storage and Handling table    |  |

|         |                 | Removed not supported features: |  |

|         |                 | > Color Decompression reference |  |

|         |                 | > DMIC reference                |  |

# Table of Contents

| Chapter 1. | Overview                                           | 1  |

|------------|----------------------------------------------------|----|

| Chapter 2. | Functional Description                             | 3  |

| 2.1 \      | /olta GPU                                          | 3  |

| 2.2        | Carmel CPU Complex                                 | 4  |

| 2.3 N      | Memory Subsystem                                   | 5  |

| 2.4 N      | Memory                                             | 6  |

| 2.5 ∖      | /ideo Input Interfaces                             | 7  |

| 2.5.1      | MIPI Camera Serial Interface (CSI)                 | 7  |

| 2.5.2      | Video Input (VI)                                   | 9  |

| 2.5.3      | Image Signal Processor (ISP)                       | 9  |

| 2.6        | Display Controller                                 | 10 |

| 2.6.1      | HDMI and DisplayPort Interfaces                    | 12 |

| 2.6.2      | Embedded DisplayPort (eDP)                         | 14 |

| 2.7 H      | High-Definition Audio-Video Subsystem              | 15 |

| 2.7.1      | Multi-Standard Video Decoder                       | 15 |

| 2.7.2      | Multi-Standard Video Encoder                       | 16 |

| 2.7.3      | JPEG Processing Block                              | 17 |

| 2.7.4      | Video Image Compositor (VIC)                       | 17 |

| 2.7.5      | Audio Processing Engine (APE)                      | 18 |

| 2.7.6      | High-Definition Audio (HDA)                        | 18 |

| 2.8 I      | nterface Descriptions                              | 19 |

| 2.8.1      | SD/eMMC                                            | 19 |

| 2.8.2      | Universal Serial Bus (USB)                         | 20 |

| 2.8.3      | PCI Express (PCIe)                                 | 21 |

| 2.8.4      | Serial Peripheral Interface (SPI)                  | 23 |

| 2.8.5      | Universal Asynchronous Receiver/Transmitter (UART) | 26 |

| 2.8.6      | Controller Area Network (CAN)                      | 27 |

| 2.8.7      | Inter-Chip Communication (I2C)                     | 28 |

| 2.8.8      | Inter-IC Sound (I2S)                               | 29 |

| 2.8.9      | Gigabit Ethernet                                   | 30 |

| 2.8.10     | Fan                                                | 31 |

| 2.8.11     | Pulse Width Modulator (PWM)                        | 31 |

| 2.9        | Deep Learning Accelerator (DLA)                    | 32 |

| 2.10 F     | Programmable Vision Accelerator (PVA)              | 33 |

| Chapter 3. | Power and System Management                        | 34 |

| 3.1.1      | Power Rails                                        |    |

| 3.1.2      | Power Domains/Islands                              |    |

| 3.1.3      | Power Management Controller (PMC)                  | 35 |

| 3.1.4      | Resets                                             |    |

| 3.1.5     | PMIC_BBATT                                            | 35 |

|-----------|-------------------------------------------------------|----|

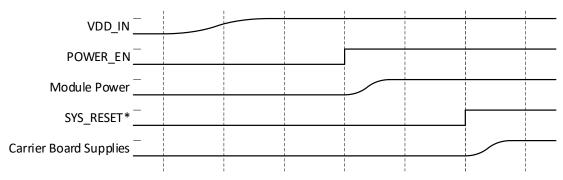

| 3.2       | Power Sequencing                                      | 36 |

| 3.2.1     | Power Up                                              | 36 |

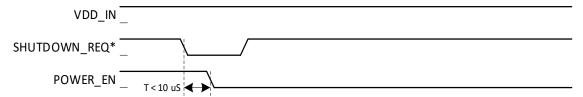

| 3.2.2     | Power Down                                            | 37 |

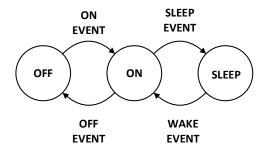

| 3.3       | Power States                                          | 37 |

| 3.3.1     | ON State                                              | 38 |

| 3.3.2     | OFF State                                             | 38 |

| 3.3.3     | SLEEP State                                           | 39 |

| 3.4       | Thermal and Power Monitoring                          | 39 |

| 3.5       | Overcurrent Throttling                                | 39 |

| Chapter 4 | . Pin Definitions                                     | 40 |

| 4.1       | Power-on Reset Behavior                               | 40 |

| 4.2       | Sleep Behavior                                        | 41 |

| 4.3       | GPIO                                                  | 41 |

| 4.4       | Pin List                                              | 42 |

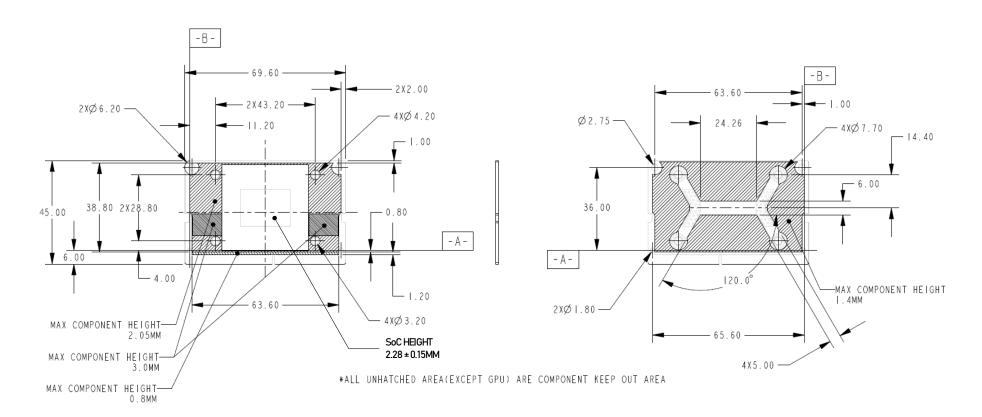

| Chapter 5 | . Electrical, Mechanical, and Thermal Characteristics | 45 |

| 5.1       | Operating and Absolute Maximum Ratings                | 45 |

| 5.2       | Digital Logic                                         | 46 |

| 5.3       | Environmental and Mechanical Screening                | 47 |

| 5.4       | Storage and Handling                                  | 48 |

| 5.5       | Package Drawing and Dimensions                        | 49 |

# List of Figures

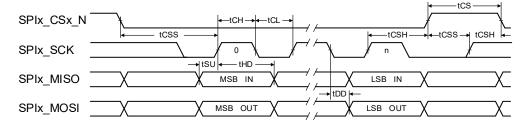

| Figure 2-1: SPI Master Timing Diagram                | 24 |

|------------------------------------------------------|----|

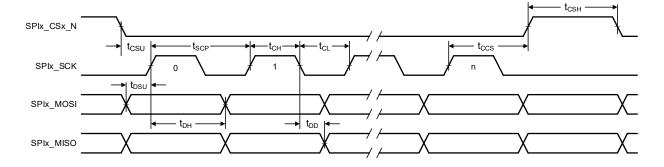

| Figure 2-2: SPI Slave Timing Diagram                 | 25 |

| Figure 3-1: Power-up Sequence                        | 37 |

| Figure 3-2: Power Down Sequence                      | 37 |

| Figure 3-3: Power State Transition Diagram           | 38 |

|                                                      |    |

| List of Tables                                       |    |

|                                                      |    |

| Table 2-1: GPU Operation                             |    |

| Table 2-2: CPU Operation                             |    |

| Table 2-3: LPDDR4x Memory Bus                        | 6  |

| Table 2-4: CSI Pin Descriptions                      |    |

| Table 2-5: Camera Pin Descriptions                   | 9  |

| Table 2-5: HDMI/DisplayPort/eDP Pin Descriptions     | 13 |

| Table 2-6: Video Decoder Standards                   | 15 |

| Table 2-7: Video Encoder Standards                   | 16 |

| Table 2-8: SD/SDIO Pin Descriptions                  | 20 |

| Table 2-9: USB 2.0 Pin Descriptions                  | 21 |

| Table 2-10: USB 3.1 Pin Descriptions                 | 21 |

| Table 2-11: PCIe Pin Descriptions                    | 22 |

| Table 2-12: SPI Pin Descriptions                     | 24 |

| Table 2-13: SPI Master Timing Parameters             | 24 |

| Table 2-14: SPI Slave Timing Parameters              | 25 |

| Table 2-15: UART Pin Descriptions                    | 26 |

| Table 2-16: CAN Pin Descriptions                     | 28 |

| Table 2-17: I2C Pin Descriptions                     | 28 |

| Table 2-18: TDM Timing Parameters (Slave Mode)       | 29 |

| Table 2-19: TDM Timing Parameters (Master Mode)      | 30 |

| Table 2-20: I2S Pin Descriptions                     |    |

| Table 2-21: Gigabit Ethernet Pin Descriptions        | 31 |

| Table 2-22: PWM Pin Descriptions                     | 32 |

| Table 2-23: DLA Clock                                | 32 |

| Table 2-24: PVA Clock Operation                      |    |

| Table 3-1: Power and System Control Pin Descriptions | 34 |

| Table 3-2: PMIC_BBAT Pin Descriptions                |    |

| Table 3-3: OFF State Events                          |    |

| Table 3-4: SLEEP and WAKE Events                     |    |

| Table 4-1: GPIO Pin Descriptions                     | 41 |

|                                                      |    |

| Table 5-1: Recommended Operating Conditions          | 45 |

|------------------------------------------------------|----|

| Table 5-2: Absolute Maximum Ratings4                 | 45 |

| Table 5-3: CMOS Pin Type DC Characteristics4         | 46 |

| Table 5-4: Open Drain Pin Type DC Characteristics4   | 46 |

| Table 5-5: Environmental Testing4                    | 47 |

| Table 5-6: Typical Handling and Storage Environment4 | 48 |

# **Chapter 1. Overview**

### **NVIDIA Jetson Xavier NX Modules:**

| Module                | Description                                       |

|-----------------------|---------------------------------------------------|

| Jetson Xavier NX      | Volta GPU + Carmel CPU + 8GB LPDDR4x + 16GB eMMc  |

| Jetson Xavier NX 16GB | Volta GPU + Carmel CPU + 16GB LPDDR4x + 16GB eMMc |

**Note:** References to Jetson Xavier NX also apply to Jetson Xavier NX 16GB except where explicitly noted.

| Description                                                                                                                                                                                                                                                                                                                                                                                                                           | Operation/Performance                                      |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--|--|--|--|

| Al Performance                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                            |  |  |  |  |

| Up to:                                                                                                                                                                                                                                                                                                                                                                                                                                | 21 TOPs (INT8)                                             |  |  |  |  |

| Volta GPU                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                            |  |  |  |  |

| 384 NVIDIA® CUDA® cores   48 Tensor cores   End-to-end I<br>ES 3.2   Vulkan™ 1.1°   CUDA 11.4⁺                                                                                                                                                                                                                                                                                                                                        | ossless compression   Tile Caching   OpenGL® 4.6+   OpenGL |  |  |  |  |

| Maximum Operating Frequency (up to):                                                                                                                                                                                                                                                                                                                                                                                                  | 1100 MHz                                                   |  |  |  |  |

| Carmel CPU                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                            |  |  |  |  |

| Armv8.2 (64-bit) heterogeneous multi-processing (HMP) CPU architecture   3x dual-core CPU clusters (six NVIDIA Carmel processor cores) connected by a high-performance system coherency interconnect fabric   L3 Cache: 4 MB (shared across all clusters)  NVIDIA Carmel (Dual-Core) Processor: L1 Cache: 128 KB L1 instruction cache (I-cache) per core; 64 KB L1 data cache (D-cache) per core   L2 Unified Cache: 2 MB per cluster |                                                            |  |  |  |  |

| Maximum Operating Frequency (up to):                                                                                                                                                                                                                                                                                                                                                                                                  | 1900 MHz                                                   |  |  |  |  |

| Memory Subsystem                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                            |  |  |  |  |

| Memory Size: 8GB (Xavier NX) with 128-bit LPDDR4x DRAM; 16GB (Xavier NX 16GB) with 128-bit LPDDR4x DRAM   Secure External Memory Access Using TrustZone® Technology   System MMU                                                                                                                                                                                                                                                      |                                                            |  |  |  |  |

| Maximum Operating Frequency (up to): 1866 MHz                                                                                                                                                                                                                                                                                                                                                                                         |                                                            |  |  |  |  |

| HD Video                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                            |  |  |  |  |

| Decode                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                            |  |  |  |  |

### Description

### **Operation/Performance**

Supported Standards: H.265, H.264, VP9, VP8, MPEG-4, MPEG-2, VC-1 (see Multi-Standard Video Decoder section for detailed description)

#### **Encode**

Supported Standards: H.265, H.264, VP9 (see Multi-Standard Video Encoder section for detailed description)

#### **Display Controller Subsystem**

Two multi-mode (eDP/DP/HDMI) Serial Output Resources (SOR) eDP 1.4a | DP 1.4 | HDMI 2.0a/b

Maximum Resolution eDP/DP/HDMI

(up to) 3840x2160 at 60 Hz (up to 36 bpp)

### Audio Subsystem

Dedicated programmable audio processor | Arm Cortex A9 with NEON | PDM in/out | Industry-standard High-Definition Audio (HDA) controller provides a multi-channel audio path to the HDMI® interface

#### Networking

10/100/1000 Gigabit Ethernet | Media Access Controller (MAC)

#### **Imaging**

14 lanes (3 x4 or 6 x2) MIPI CSI-2 | D-PHY 1.2 (2.5 Gb/s per pair, total up to 30 Gbps)

### Storage

16 GB eMMC 5.1 Flash Storage | Bus Width: 8-bit | Maximum Bus Frequency: 200 MHz (HS400)

### **Peripheral Interfaces**

USB: xHCl host controller with integrated PHY (up to) 1 x USB 3.1, 3 x USB 2.0

PCIe: 1x1 (GEN3) + 1x4 (GEN4) | SD/MMC controller (supporting eMMC 5.1, SD 4.0, SDHOST 4.0 and SDIO 3.0)

**Audio:** 2 x I2S **UART:** 3 x UART **CAN:** 1 x CAN **SPI:** 2 x SPI **I2C:** 4 x I2C

**PWM:** 4 x PWM outputs

**GPIO:** 15 x GPIOs

#### Mechanical

Module Size: 69.6 mm x 45 mm | 260 pin SO-DIMM Connector

#### **Operating Requirements**

Temp. Range (TJ)\*: -25°C - 90°C | Supported Power Input: 5V | Supported Power Modes: 10W/15W/20W

#### Notes:

- Refer to the Software Features section of the latest L4T Development Guide for a list of supported features; all features may not be available.

- Product is based on a published Khronos Specification and is expected to pass the Khronos Conformance Process. Current conformance status can be found at <a href="https://www.khronos.org/conformance">www.khronos.org/conformance</a>.

- \* See the Jetson Xavier NX Thermal Design Guide for details

# **Chapter 2. Functional Description**

NVIDIA® Jetson Xavier™ NX brings AI supercomputer performance to the edge in a compact system-on-module (SOM) which is smaller than a credit card. Jetson Xavier NX is built around a low-power version of the NVIDIA Xavier SoC, combining the NVIDIA Volta™ GPU architecture with 64-bit operating capability, integrated advanced multi-function video and image processing, and NVIDIA Deep Learning Accelerators.

Compute performance up to 21 TOPs (at 15W and 20W) enables the Jetson Xavier NX to run multiple neural networks in parallel and process data from multiple high-resolution sensors simultaneously. It also offers a unique combination of performance and power advantages with a rich set of I/Os, from high-speed CSI and PCIe to low-speed I<sup>2</sup>Cs and GPIOs, allowing embedded and edge computing devices that demand increased performance but are constrained by size, weight, and power budgets.

## 2.1 Volta GPU

The Graphics Processing Cluster (GPC) is a dedicated hardware block for computing, rasterization, shading, and texturing of most of the GPU's core graphics functions. The GPC is comprised of Texture Processing Clusters (TPC), with each TPC containing two Streaming Multiprocessor (SM) units, and a Raster Engine. The SM unit creates, manages, schedules, and executes instructions from many threads in parallel. Raster operators (ROPs) continue to be aligned with L2 cache slices and memory controllers. The SM geometry and pixel processing performance make it highly suitable for rendering advanced user interfaces, while the efficiency of the Volta GPU enables this performance on devices with power-limited environments.

Each SM is partitioned into four separate processing blocks (referred to as SMPs), each SMP contains its own instruction buffer, scheduler, CUDA cores, and Tensor cores. Inside each SMP, CUDA cores perform pixel/vertex/geometry shading and physics/compute calculations, and each Tensor core provides a 4x4x4 matrix processing array to perform mixed-precision fused multiply-add (FMA) mathematical operations. Texture units perform texture filtering and load/store units fetch and save data to memory. Special Function Units (SFUs) handle transcendental and graphics interpolation instructions. Finally, the PolyMorph Engine handles vertex fetch, tessellation, viewport transform, attribute setup, and stream output.

- > End-to-end lossless compression

- Tile Caching

- Support for OpenGL 4.6, OpenGL ES 3.2, Vulkan 1.1

- Adaptive Scalable Texture Compression (ASTC) LDR profile supported

- CUDA support

- Iterated blend, ROP OpenGL-ES blend modes

- 2D BLIT from 3D class avoids channel switch

- 2D color compression

- Constant color render SM bypass

- 2x, 4x, 8x MSAA with color and Z compression

- Non-power of 2D and 3D textures, FP16 texture filtering

- FP16 shader support

- Geometry and Vertex attribute instancing

- Parallel pixel processing

- Early-z reject: Fast rejection of occluded pixels acts as multiplier on pixel shader and texture performance while saving power and bandwidth

- Video protection region

- Power saving: Multiple levels of clock gating for linear scaling of power

Table 2-1: GPU Operation

| Module                | CUDA Cores | Tensor Cores | Power Mode | Operating Frequency per Core (up to) |

|-----------------------|------------|--------------|------------|--------------------------------------|

| Jetson Xavier NX,     | 384        | 48           | 10W        | 800 MHz                              |

| Jetson Xavier NX 16GB |            |              | 15W        | 1100 MHz                             |

|                       |            |              | 20W        | 1100 MHz                             |

### Carmel CPU Complex 2.2

The CPU complex (CCPLEX) is comprised of three Carmel dual-core CPU clusters in a coherent multi-processor configuration. A high-performance System Coherency Fabric (SCF) connects all CPU clusters enabling simultaneous operation of all CPU cores (as needed) for a true heterogeneous multi-processing (HMP) environment.

#### Features include:

- **NVIDIA Dynamic Code Optimization**

- 10-wide Superscalar architecture

- Dynamic branch prediction with a Branch Target Buffer and Global History Buffer RAMs, a return stack buffer, and an indirect predictor

- Full implementation of Armv8.2 ISA compliant architecture including:

- Armv8 TrustZone

- Armv8.0 Crypto ISA

- Trusted Memory

- Armv8.2-FP16 support

- > 128 KB 4-way-associative parity protected L1 instruction cache per core

- > 64 KB 4-way-associative parity protected L1 data cache per core

- 2 MB 16-way-associative ECC protected L2 cache per CPU cluster

- > 4 MB 16-way-associative ECC protected L3 cache (shared across all clusters)

- > Performance Monitoring

- > Interface to an external Generic Interrupt Controller (vGIC-400)

- > Support for power management with multiple power domains

Table 2-2: CPU Operation

| Module                | Power Mode | CPU Cores | CPU Maximum Frequency |

|-----------------------|------------|-----------|-----------------------|

| Jetson Xavier NX,     | 10W        | 2-core    | 1.5 GHz               |

| Jetson Xavier NX 16GB |            | 4-core    | 1.2 GHz               |

|                       | 15W        | 2-core    | 1.9 GHz               |

|                       |            | 4/6-core  | 1.4 GHz               |

|                       | 20W        | 2-core    | 1.9 GHz               |

|                       |            | 4/6-core  | 1.4 GHz               |

# 2.3 Memory Subsystem

The Memory Subsystem (MSS) provides access to local DRAM, SysRAM, and provides a SyncPoint Interface for inter-processor signaling. The MSS supports full-speed I/O coherence by routing requests through a scalable coherence fabric. It also supports a comprehensive set of safety and security mechanisms.

Structurally, the MSS consists of:

- 1. MSS Data Backbone routes requests from clients to the MSS Hub and responses from MSS Hub to the clients.

- 2. MSS Hub receives and arbitrates among client requests, performs SMMU translation, and sends requests to MCF.

- 3. Memory Controller Fabric (MCF) performs security checks, feeds I/O coherent requests to the Scalable Coherence Fabric (SCF), and directs requests to the multiple memory channels.

- 4. Memory Controller (MC) Channels row sorter/arbiter and DRAM controllers.

- 5. DRAM I/O channel-to-pad fabric, DRAM I/O pads, and PLLs.

Jetson Xavier NX integrates a 128-bit wide LPDDR4x memory interface implemented as four 32-bit channels with x16 sub-partitions. The memory controller provides a single read or write command, plus a row address to both sub-partitions in the channel to transfer 64 bytes. It also provides three independent column address bits to each sub-partition, allowing it access different 32-byte sectors of a GOB between the sub-partitions. It provides connections between a wide variety of clients, supporting their bandwidth, latency, quality-of-service needs, and any

special ordering requirements that are needed. The MSS supports a variety of security and safety features and address translation for clients that use virtual addresses.

#### Features:

- > LPDDR4x: x32 DRAM chips

- 128-bit wide data bus

- Low latency path and fast read/response path support for the CPU complex cluster

- Support for low-power modes:

- Software controllable entry/exit from self-refresh, power down, and deep power down

- Hardware dynamic entry/exit from power down, self-refresh

- Pads use DPD mode during idle periods

- High-bandwidth interface to the integrated Volta GPU

- Full-speed I/O coherence with bypass for Isochronous (ISO) traffic

- > System Memory-Management Unit (SMMU) for address translation based on the Arm SMMU-500

- > High-bandwidth PCIe ordered writes

- AES-XTS encryption with 128-bit key

#### 24 Memory

The Memory Controller (MC) maximizes memory utilization while providing minimum latency access for critical CPU requests. An arbiter is used to prioritize requests, optimizing memory access efficiency and utilization and minimizing system power consumption. The MC provides access to main memory for all internal devices. It provides an abstract view of memory to its clients via standardized interfaces, allowing the clients to ignore details of the memory hierarchy. It optimizes access to shared memory resources, balancing latency and efficiency to provide best system performance, based on programmable parameters.

#### Features:

- TrustZone (TZ) Secure and OS-protection regions

- System Memory Management Unit

- Dual CKE signals for dynamic power down per device

- Dynamic Entry/Exit from Self-Refresh and Power Down states

### Table 2-3: LPDDR4x Memory Bus

| Module                | Size  | Maximum Bandwidth | Maximum Bus Frequency |

|-----------------------|-------|-------------------|-----------------------|

| Jetson Xavier NX      | 8 GB  | 59.7 GB/s         | 1866 MHz              |

| Jetson Xavier NX 16GB | 16 GB | 59.7 GB/s         | 1866 MHz              |

# 2.5 Video Input Interfaces

# 2.5.1 MIPI Camera Serial Interface (CSI)

#### **Standard**

MIPI CSI 2.0 Receiver specification

MIPI D-PHY® v1.2 Physical Layer specification

The NVIDIA Camera Serial Interface (NVCSI) works with the Video Input (VI) unit to capture an image from a sensor, where NVCSI is a source of pixel data to VI. NVCSI works in streaming mode while VI captures the required frames using a single-shot mode of operation. All sync point generation for software is handled at VI; the delay between NVCSI and VI is negligible in software terms. NVCSI does not have a direct memory port, instead it sends the pixel data to memory through the VI.

Fifth-generation NVIDIA camera solution (NVCSI 2.0, VI 5.0, and ISP 5.0) provides a combination host that supports enhanced MIPI D-PHY (with lane deskew support) physical layer options in three 4-lane or six 2-lane configurations; or combinations of these. Each lane can support up to 16 virtual channels (VC) and supports data type interleaving.

- > Virtual Channel Interleaving: VCs are defined in the CSI-2 specification and are useful when supporting multiple camera sensors. With the VC capability, a one-pixel parser (PP) can deinterleave up to 16 image streams.

- > Data Type Interleaving: In HDR line-by-line mode, the sensor can output long/short exposure lines using the same VC and a different programmable data type (DT).

- Frequency Target: The parallel pixel processing rate, measured in pixels-per-clock (PPC), is increased to allow higher throughput and lower clock speeds. To support higher bandwidth without increasing the operating frequency, the host processes multiple pixels in one clock. NVCSI is capable of processing four PPCs when bits-per-pixel (BPP) is greater than 16, and eight PPC when BPP is less than or equal to 16.

- > With the new streaming mode in NVCSI, one PP can handle all traffic (embedded data and image data) from one camera device, including 16 VCs.

- > Supports the MIPI D-PHY v1.2 physical layer option:

- MIPI D-PHY supports up to 2.5 Gbits/sec per pair, for an aggregate bandwidth of 30 Gbps from 12 pairs

- > Based on MIPI CSI-2 v2.0 protocol stack

- > Includes six-pixel parsers (PP)

- Supports up to 16 virtual channels per active PP

- Supported input data formats:

- RGB: RGB888, RGB666, RGB565, RGB555, RGB444

- YUV: YUV422-8b, YUV420-8b (legacy), YUV420-8b

- RAW: RAW6, RAW7, RAW8, RAW10, RAW12, RAW14, RAW16, RAW20

- DPCM (predictor 1): 14-10-14, 14-8-14, 12-8-12, 12-7-12, 12-6-12, 12-10-12, 10-8-10, 10-7-10, 10-6-10 (Predictor 2 not supported)

- > Data type interleave support

Table 2-4: CSI Pin Descriptions

| Pin# | Signal Name | Description           | Direction | Pin Type   |

|------|-------------|-----------------------|-----------|------------|

| 10   | CSIO_CLK_N  | Camera, CSI 0 Clock-  | Input     | MIPI D-PHY |

| 12   | CSIO_CLK_P  | Camera, CSI 0 Clock+  | Input     | MIPI D-PHY |

| 4    | CSIO_DO_N   | Camera, CSI 0 Data 0- | Input     | MIPI D-PHY |

| 6    | CSIO_DO_P   | Camera, CSI 0 Data 0+ | Input     | MIPI D-PHY |

| 16   | CSIO_D1_N   | Camera, CSI 0 Data 1- | Input     | MIPI D-PHY |

| 18   | CSIO_D1_P   | Camera, CSI 0 Data 1+ | Input     | MIPI D-PHY |

| 9    | CSI1_CLK_N  | Camera, CSI 1 Clock-  | Input     | MIPI D-PHY |

| 11   | CSI1_CLK_P  | Camera, CSI 1 Clock+  | Input     | MIPI D-PHY |

| 3    | CSI1_D0_N   | Camera, CSI 1 Data 0- | Input     | MIPI D-PHY |

| 5    | CSI1_D0_P   | Camera, CSI 1 Data 0+ | Input     | MIPI D-PHY |

| 15   | CSI1_D1_N   | Camera, CSI 1 Data 1- | Input     | MIPI D-PHY |

| 17   | CSI1_D1_P   | Camera, CSI 1 Data 1+ | Input     | MIPI D-PHY |

| 28   | CSI2_CLK_N  | Camera, CSI 2 Clock-  | Input     | MIPI D-PHY |

| 30   | CSI2_CLK_P  | Camera, CSI 2 Clock+  | Input     | MIPI D-PHY |

| 22   | CSI2_D0_N   | Camera, CSI 2 Data 0- | Input     | MIPI D-PHY |

| 24   | CSI2_D0_P   | Camera, CSI 2 Data 0+ | Input     | MIPI D-PHY |

| 34   | CSI2_D1_N   | Camera, CSI 2 Data 1- | Input     | MIPI D-PHY |

| 36   | CSI2_D1_P   | Camera, CSI 2 Data 1+ | Input     | MIPI D-PHY |

| 27   | CSI3_CLK_N  | Camera, CSI 3 Clock-  | Input     | MIPI D-PHY |

| 29   | CSI3_CLK_P  | Camera, CSI 3 Clock+  | Input     | MIPI D-PHY |

| 21   | CSI3_D0_N   | Camera, CSI 3 Data 0- | Input     | MIPI D-PHY |

| 23   | CSI3_D0_P   | Camera, CSI 3 Data 0+ | Input     | MIPI D-PHY |

| 33   | CSI3_D1_N   | Camera, CSI 3 Data 1- | Input     | MIPI D-PHY |

| 35   | CSI3_D1_P   | Camera, CSI 3 Data 1+ | Input     | MIPI D-PHY |

| 52   | CSI4_CLK_N  | Camera, CSI 4 Clock-  | Input     | MIPI D-PHY |

| 54   | CSI4_CLK_P  | Camera, CSI 4 Clock+  | Input     | MIPI D-PHY |

| 46   | CSI4_D0_N   | Camera, CSI 4 Data 0- | Input     | MIPI D-PHY |

| 48   | CSI4_D0_P   | Camera, CSI 4 Data 0+ | Input     | MIPI D-PHY |

| 58   | CSI4_D1_N   | Camera, CSI 4 Data 1- | Input     | MIPI D-PHY |

| 60   | CSI4_D1_P   | Camera, CSI 4 Data 1+ | Input     | MIPI D-PHY |

| 40   | CSI4_D2_N   | Camera, CSI 4 Data 2- | Input     | MIPI D-PHY |

| 42   | CSI4_D2_P   | Camera, CSI 4 Data 2+ | Input     | MIPI D-PHY |

| 64   | CSI4_D3_N   | Camera, CSI 4 Data 3- | Input     | MIPI D-PHY |

|      |             |                       |           |            |

| Pin# | Signal Name | Description           | Direction | Pin Type   |

|------|-------------|-----------------------|-----------|------------|

| 66   | CSI4_D3_P   | Camera, CSI 4 Data 3+ | Input     | MIPI D-PHY |

| 76   | DSI_CLK_N   | Camera, CSI 5 Clock-  | Input     | MIPI D-PHY |

| 78   | DSI_CLK_P   | Camera, CSI 5 Clock+  | Input     | MIPI D-PHY |

| 70   | DSI_DO_N    | Camera, CSI 5 Data 0- | Input     | MIPI D-PHY |

| 72   | DSI_DO_P    | Camera, CSI 5 Data 0+ | Input     | MIPI D-PHY |

| 82   | DSI_D1_N    | Camera, CSI 5 Data 1- | Input     | MIPI D-PHY |

| 84   | DSI_D1_P    | Camera, CSI 5 Data 1+ | Input     | MIPI D-PHY |

Table 2-5: Camera Pin Descriptions

| Pin# | Signal Name | Description                                                    | Direction | Pin Type          |

|------|-------------|----------------------------------------------------------------|-----------|-------------------|

| 213  | CAM_I2C_SCL | Camera I2C Clock. 2.2k $\Omega$ pull-up to 3.3V on the module. | Bidir     | Open Drain – 3.3V |

| 215  | CAM_I2C_SDA | Camera I2C Data. $2.2k\Omega$ pull-up to $3.3V$ on the module. | Bidir     | Open Drain – 3.3V |

| 116  | CAMO_MCLK   | Camera O Reference Clock                                       | Output    | CMOS – 1.8V       |

| 114  | CAMO_PWDN   | Camera O Powerdown or GPIO                                     | Output    | CMOS – 1.8V       |

| 122  | CAM1_MCLK   | Camera 1 Reference Clock                                       | Output    | CMOS – 1.8V       |

| 120  | CAM1_PWDN   | Camera 1 Powerdown or GPIO                                     | Output    | CMOS – 1.8V       |

#### 2.5.2 Video Input (VI)

The VI block receives data from the CSI receiver and prepares it for presentation to system memory or the dedicated image signal processor execution resources. The VI block provides formatting for RGB, YCbCr, and raw Bayer data in support of several camera user models. These models include single and multi-camera systems, which may have up to six active streams. The input streams are obtained from MIPI compliant CMOS sensor camera modules.

#### Image Signal Processor (ISP) 2.5.3

The ISP module takes data from the VI/CSI module or memory in raw Bayer format and processes it to YUV output. The imaging subsystem supports raw (Bayer) image sensors up to 24 million pixels. Advanced image processing is used to convert input to YUV data and remove artifacts introduced by high-megapixel CMOS sensors and optics with up to 30-degree CRA.

- Flexible post-processing architecture for supporting custom computer vision and computational imaging operations

- Bayer domain hardware noise reduction

- Per-channel black-level compensation

- High-order lens-shading compensation

- 3x3 color transform

- > Bad pixel correction

- > Programmable coefficients for de-mosaic with color artifact reduction Color artifact reduction: a two-level (horizontal and vertical) low-pass filtering scheme that is used to reduce/remove any color artifacts that may result from Bayer signal processing and the effects of sampling an image.

- > Enhanced down scaling quality

- > Edge enhancement

- > Color and gamma correction

- > Programmable transfer function curve

- > Color-space conversion (RGB to YUV)

- > Image statistics gathering (per-channel)

- Two 256-bin image histograms

- Up to 4,096 local region averages

- AC flicker detection (50 Hz and 60 Hz)

- Focus metric block

# 2.6 Display Controller

The Jetson Xavier NX integrates a Unified Display Controller (based on the NVIDIA NVDisplay architecture) and two independent display outputs. The Display Controller includes a Pixel Processing Engine that fetches pixel data to be processed from DRAM and generates up to six windows of rasterized display-ready pixel data. The instructions for processing the pixel data are captured by the display controller's Front End (FE) logic, which then generates the individual controls for the various stages of pixel processing.

The pixel data to be processed are fetched in the Isochronous Memory Hub (IsoHub) then go through the specified pixel processing, including merging the cursor, in four pipe stages: Pre-Composition (Pre-comp); Composition (Comp); Post-Composition (Post-comp); and Raster Generation (RG). The rasterized display-ready pixel data are available for the separate panels/devices (referred to as display heads) and are fed through a multi-channel crossbar structure to the Serial Output Resources (SOR) in the Display Interface for the standard display output format, i.e., DP (Display Port) and High-Definition Multimedia Interface (HDMI).

Each of the display heads can be run at an independent clock rate and each can drive a different display resolution. Each of the six display windows (A, B, C, D, E, F) can be arbitrarily assigned to any of the display Heads as required, then connected to any one of the display heads for the desired output format.

- Integrated HDCP key storage, no external SecureROM required

- > Six windows that can be assigned to any Head

- One special-purpose TrustZone protected window on HeadO

- > Maximum raster size: 32768 x 32768

- > Maximum active region: 8192 x 8192

- Maximum input surface size: 32768 x 32768

- Maximum fetched size: 8192 x 8192

- Input surface color formats:

- 16-bit RGB: R4G4B4A4, R5G6B5, A1R5G5B5, and R5G5B5A1

- 24-bit RGB: A8R8G8B8, X8R8G8B8, A8B8G8R8, and X8B8G8R8

- 32-bit RGB: A2R10G10B10, A2B10G10R10, X2BL10GL10RL10\_XRBIAS, and X2BL10GL10RL10\_XVYCC

- 64-bit RGB: R16\_G16\_B16\_A16\_NVBIAS, and R16\_G16\_B16\_A16

- Packed YUV 422: Y8 U8 Y8 V8 N422, and U8 Y8 V8 Y8 N422

- Semi Planar YUV 422 (8, 10, 12 bpc):

- Y8 V8U8 N422, Y8 V8U8 N422R

- Y10\_V10U10\_N422, Y10\_V10U10\_N422R

- Y12\_V12U12\_N422, Y12\_V12U12\_N422R

- Semi-planar YUV 420 (8, 10, 12 bpc):

- Y8\_V8U8\_N420\*

- Y10\_V10U10\_N420\*

- Y12\_V12U12\_N420\*

- Semi-planar YUV 444 (8, 10, 12 bpc):

- Y8\_V8U8\_N444

- Y10\_V10U10\_N444

- Y12\_V12U12\_N444

- Planar YUV 420 (8, 10, 12 bpc):

- Y8 U8 V8 N420

- Y10\_U10\_V10\_N420

- Y12\_U12\_V12\_N420

- Planar YUV 444 (8, 10, 12 bpc):

- Y8 U8 V8 N444

- Y10 U10 V10 N444

- Y12\_U12\_V12\_N444

- Pipeline depth

- 16-bpc, [-1.5, 2.5] range (two range extension bits): De-gamma will clip to 0,1 immediately on the input

- Vsync (VCOUNTER) and immediate (HCOUNTER) flip modes

- Immediate flip supported for RGB only

- Immediate flips occur at the second 8-line boundary after the current line

Note: Cursor cannot be enabled on a Head unless the Head has at least one window group attached. The window group does not need to be enabled.

TrustZone cannot be enabled unless HeadO has at least one window group attached. This does not need to be enabled.

Color formats marked with an asterisk (\*) are programmed as Y\_UV in the display manuals, and then byte-swapped later to be Y\_VU.

10-bpc and 12-bpc YUV color formats are packed into 16-bpc containers. This effectively limits immediate flips to no faster than one every 16 lines.

#### 2.6.1 HDMI and DisplayPort Interfaces

| Standard                                                                     | Notes                                                                                              |

|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| High-Definition Multimedia Interface (HDMI)<br>Specification, version 2.0a/b | Scrambling support Clock/4 support (1/40 bit-rate clock) HDMI 1.4 (up to 340 MHz pixel clock rate) |

|                                                                              | HDMI 2.0 (up to 594 MHz pixel clock rate)                                                          |

| VESA DisplayPort Standard Version 1.4                                        |                                                                                                    |

A standard DP 1.4 or High-Definition Multimedia Interface (HDMI) 2.0a/b interface is supported. These share the same set of interface pins, so either DisplayPort (DP) or HDMI can be supported natively. Each output collects the output of a display pipeline from the display controller, formats/encodes that output (to a desired format), and then streams it to an output device. Each output can provide an interface to an external device; each output can drive only a single output device at any given time. HDMI support provides a method of transferring both audio and video data; the SOR receives video from the display controller and audio from a separate high-definition audio (HDA) controller, it combines and transmits them as appropriate.

Note: A single CEC controller is shared between the two HDMI/DP interfaces. Both DPO and DP1 support either DP or HDMI.

#### Features:

- DisplayPort

- Multichannel audio from HDA controller, up to eight channels, 96 kHz, 24-bit

- DP1.4 supports HBR3 at 8.1 Gbps

- (up to) 540 MHz pixel clock rate (i.e., 1.62 GHz for RBR, 2.7 GHz for HBR, 5.4 GHz for HBR2, and 8.1 Gbps for HBR3.

- 8b/10b encoding support

- External dual-mode standard support

- Audio streaming support

#### HDMI

- (up to) 594 MHz pixel clock

- 8/12 bpc RGB and YUV444

- 8/10/12 bpc YUV422

- 8 bpc YUV420 (10/12 bpc YUV frame buffers should be output as YUV422)

- HDMI Vendor-Specific Info frame (VSI) packet transmission

- On HDMI, multichannel audio from HDA controller, up to eight channels, 192 kHz, 24-bit.

- Fuse calibration information for HDMI analog parameter(s)

- 1080i output on HDMI

- DP or HDMI connectors via appropriate external level shifting

- > HDCP 2.2 and 1.4 over either DP or HDMI Note: refer to NVIDIA software release notes for detailed specifications.

- > External Dual Mode standard (DP2HDMI passive or active adapters and adapter discovery)

- > Generic info frame transmission

- > Frame-packed 3D stereo mode

Table 2-6: HDMI/DisplayPort/eDP Pin Descriptions

| Pin# | Signal Name | Description                                | Direction | Pin Type                                                                             |

|------|-------------|--------------------------------------------|-----------|--------------------------------------------------------------------------------------|

| 39   | DP0_TXD0_N  | DisplayPort O Lane O or HDMI Lane 2-       | Output    | AC-Coupled on carrier board                                                          |

| 41   | DP0_TXD0_P  | DisplayPort 0 Lane 0 or HDMI Lane 2+       | Output    | AC-Coupled on carrier board                                                          |

| 45   | DP0_TXD1_N  | DisplayPort 0 or HDMI Lane 1-              | Output    | AC-Coupled on carrier board                                                          |

| 47   | DP0_TXD1_P  | DisplayPort 0 or HDMI Lane 1+              | Output    | AC-Coupled on carrier board                                                          |

| 51   | DP0_TXD2_N  | DisplayPort O Lane 2- or HDMI Lane 0-      | Output    | AC-Coupled on carrier board                                                          |

| 53   | DP0_TXD2_P  | DisplayPort 0 Lane 2+ or HDMI Lane 0+      | Output    | AC-Coupled on carrier board                                                          |

| 57   | DP0_TXD3_N  | DisplayPort 0 Lane 3- or HDMI Clk<br>Lane- | Output    | AC-Coupled on carrier board                                                          |

| 59   | DP0_TXD3_P  | DisplayPort 0 Lane 3+ or HDMI Clk<br>Lane+ | Output    | AC-Coupled on carrier board                                                          |

| 90   | DP0_AUX_N   | Display Port 0 Aux- or HDMI DDC SDA        | Bidir     | AC-Coupled on Carrier Board (eDP/DP)                                                 |

| 92   | DP0_AUX_P   | Display Port 0 Aux+ or HDMI DDC SCL        | Bidir     | AC-Coupled on Carrier Board (eDP/DP)                                                 |

| 88   | DP0_HPD     | Display Port 0 or HDMI Hot Plug Detect     | Input     | CMOS – 1.8V                                                                          |

| 63   | DP1_TXD0_N  | DisplayPort 1 Lane 0 or HDMI Lane 2-       | Output    | AC-Coupled on carrier board                                                          |

| 65   | DP1_TXD0_P  | DisplayPort 1 Lane 0 or HDMI Lane 2+       | Output    | AC-Coupled on carrier board                                                          |

| 69   | DP1_TXD1_N  | DisplayPort 1 or HDMI Lane 1-              | Output    | AC-Coupled on carrier board                                                          |

| 71   | DP1_TXD1_P  | DisplayPort 1 or HDMI Lane 1+              | Output    | AC-Coupled on carrier board                                                          |

| 75   | DP1_TXD2_N  | DisplayPort 1 Lane 2- or HDMI Lane 0-      | Output    | AC-Coupled on carrier board                                                          |

| 77   | DP1_TXD2_P  | DisplayPort 1 Lane 2+ or HDMI Lane 0+      | Output    | AC-Coupled on carrier board                                                          |

| 81   | DP1_TXD3_N  | DisplayPort 1 Lane 3- or HDMI Clk<br>Lane- | Output    | AC-Coupled on carrier board                                                          |

| 83   | DP1_TXD3_P  | DisplayPort 1 Lane 3+ or HDMI Clk<br>Lane+ | Output    | AC-Coupled on carrier board                                                          |

| 98   | DP1_AUX_N   | Display Port 1 Aux- or HDMI DDC SDA        | Bidir     | AC-Coupled on Carrier Board<br>(eDP/DP) or Open-Drain, 1.8V<br>(3.3V tolerant - DDC) |

| Pin# | Signal Name | Description                            | Direction | Pin Type                                                                            |

|------|-------------|----------------------------------------|-----------|-------------------------------------------------------------------------------------|

| 100  | DP1_AUX_P   | Display Port 1 Aux+ or HDMI DDC SCL    | Bidir     | AC-Coupled on Carrier Board<br>(eDP/DP) or Open-Drain, 1.8V<br>(3.3V tolerant - DDC |

| 96   | DP1_HPD     | Display Port 1 or HDMI Hot Plug Detect | Input     | CMOS – 1.8V                                                                         |

| 94   | HDMI_CEC    | HDMI CEC                               | Bidir     | Open Drain, 1.8V                                                                    |

Note: (Resolution + Refresh Rate + Pixel Depth + Format) must be within specification limits to achieve support for desired pixel depth.

#### 2.6.2 Embedded DisplayPort (eDP)

#### **Standard**

VESA Embedded DisplayPort Standard Version 1.4a

Embedded DisplayPort (eDP) is a mixed-signal interface consisting of four differential serial output lanes and one PLL. This PLL is used to generate a high-frequency bit-clock from an input pixel clock enabling the ability to handle 10-bit parallel data per lane at the pixel rate for the desired mode. eDP modes consist of 1.6 GHz for RBR; 2.16 GHz, 2.43 GHz, and 2.7 GHz for HBR; 3.24 GHz, 4.32 GHz, 5.4 GHz for HBR2, and 8.1 Gbps for HBR3.

Note: eDP has been tested according to DP1.2b PHY CTS even though eDPv1.4 supports lower swing voltages and additional intermediate bit rates. This means the following nominal voltage levels (400mV, 600mV, 800mV, 1200mV) and data rates (RBR, HBR, HBR2) are tested. This interface can be tuned to drive lower voltage swings below 400mV and can be programmed to other intermediate bit rates as per the requirements of the panel and the system designer.

The eDP block collects pixels from the output of the display pipeline, formats/encodes them to the eDP format, and then streams them to various output devices. It drives local panels only (does not support an external DP port), and it includes a small test pattern generator and CRC generator.

#### Features:

- 1/2/4/ lane, single link

- Additional link rates (2.16, 2.43, 3.24, 4.32 Gbps)

- Enhanced framing

- Power sequencing

- Reduced auxiliary timing

- Reduced main voltage swing

- ASSR (alternate seed scrambler reset) for internal eDP panels

Note: For eDP pin information, refer to HDMI/DisplayPort/eDP Pin Descriptions.

#### 2.7 High-Definition Audio-Video Subsystem

#### **Standard**

High-Definition Audio Specification Version 1.0a

The HD Audio-Video Subsystem uses a collection of functional blocks to off-load audio and video processing activities from the CPU complex, resulting in fast, fully concurrent, and highly efficient operation. This subsystem is comprised of the following:

- (2x) Multi-standard video decoder

- (2x) Multi-standard video encoder

- JPEG processing block

- Video Image Compositor (VIC)

- Audio Processing Engine (APE)

- High-Definition Audio (HDA)

#### Multi-Standard Video Decoder 271

The Jetson Xavier NX incorporates two instances of the NVIDIA Multi-Standard Video Decoder (NVDEC). This video decoder accelerates video decode, supporting low resolution mobile content, Standard Definition (SD), High Definition (HD), and UltraHD (8K, 4K, etc.) video profiles. The video decoder is designed to be extremely power efficient without sacrificing performance. The video decoder communicates with the memory controller through the video DMA which supports a variety of memory format output options. For low power operations, the video decoder can operate at the lowest possible frequency while maintaining real-time decoding using dynamic frequency scaling techniques.

Table 2-7: Video Decoder Standards

| Standard | Profile(s)             | Resolution (Max Number of Streams)                                   | Throughput (up to)                                           |

|----------|------------------------|----------------------------------------------------------------------|--------------------------------------------------------------|

| H.264    | Baseline, Main, High,  | 2x 2160p60   6x 2160p30  <br>10x 1080p60   22x 1080p30               | 2x 740 MP/s                                                  |

|          |                        | 2x 2160p30   4x 1080p60   10x 1080p30                                | 2x 370 MP/s                                                  |

|          | two views)*            |                                                                      | (Max Throughput half for<br>YUV444 as compared to<br>YUV420) |

| HEVC     | Main, Main 10, Main 12 | 2x 4320p30   6x 2160p60   12x 2160p30  <br>22x 1080p60   44x 1080p30 | 2x 1300 MP/s                                                 |

|          | Main 444 12, MV*       | 2x 2160p60   6x 2160p30   10x 1080p60                                | 2x 650 MP/s                                                  |

|          |                        | 22x 1080p30                                                          | (Max Throughput half for<br>YUV444 as compared to<br>YUV420) |

| VP9      | Profile 0. Profile 2   | 2x 4320p30   4x 2160p60   8x 2160p30  <br>14x 1080p60   30x 1080p30  | 2x 1000 MP/s                                                 |

### Supported Video Standards - Decode:

- > Bitrates: 5-10 Mbps for 1080p | Less than 20 Mbps for 2160p

- > \*Maximum throughput is half for YUV444 compared to YUV420

- > Supports HEVC Main 12 (without monochrome)

- > Supports Main 444 12 (without YUV422/YUV400)

- > 2x 8K30, 6x 4K60, 12x 4K30 Subject to memory availability

## 2.7.2 Multi-Standard Video Encoder

The Jetson Xavier NX incorporates two instances of the NVIDIA Multi-Standard Video Encoder (NVENC). This multi-standard video encoder enables full hardware acceleration of various encoding standards. It performs high-quality video encoding operations for mobile applications such as video recording and video conferencing. The encode processor is designed to be extremely power efficient without sacrificing performance.

Table 2-8: Video Encoder Standards

| Standard                       | Profile(s)                                    | Resolution (Max Number of Streams)                     | Throughput (up to) |

|--------------------------------|-----------------------------------------------|--------------------------------------------------------|--------------------|

| H264                           | HP                                            | 2x 2160p30   4x 1080p60   10x 1080p30                  | (2x) 370 MP/s      |

|                                | UHP                                           | 2x 2160p60   4x 2160p30   10x 1080p60  <br>20x 1080p30 | (2x) 660 MP/s      |

| HEVC                           | HEVC HP 2x 2160p30   4x 1080p60   10x 1080p30 |                                                        | (2x) 350 MP/s      |

|                                | UHP                                           | 2x 2160p60   4x 2160p30   10x 1080p60   22x 1080p30    | (2x) 700 MP/s      |

| VP9 HP 2x 2160p30   6x 1080p60 |                                               | 2x 2160p30   6x 1080p60   12x 1080p30                  | (2x) 410 MP/s      |

|                                | UHP                                           | 2x 2160p30   6x 1080p60   14x 1080p30                  | (2x) 445 MP/s      |

### Supported Video Standards - Encode:

- > Bitrates: 5-10 Mbps for 1080p | Less than 20 Mbps for 2160p

- > Maximum throughput is half for YUV444 compared to YUV420

**Note:** A/V codec, post-processing, and containers support are subject to software support; refer to NVIDIA software release notes for detailed specifications. Additional audio codecs may be supported using 3rd parties.

- > Timestamp for Audio/Video Sync

- CBR and VBR rate control (supported in firmware)

- > Programmable intra-refresh for error resiliency

- Macro-block based and bit based packetization (multiple slice)

- Motion estimation (ME) only mode

# 2.7.3 JPEG Processing Block

The JPEG processing block is responsible for JPEG (de)compression calculations (based on JPEG still image standard), image scaling, decoding (YUV420, YUV422H/V, YUV444, YUV400), and color space conversion (RGB to YUV; decode only).

### Input (encode) formats:

- > Pixel width: 8 bpc

- > Subsample format: YUV420

- > Resolution up to 16K x 16K

- > Pixel pack format

- Semi-planar/planar for 420

- Output (decode) formats:

- > Pixel width 8 bpc

- Resolution up to 16K x 16K

- Pixel pack format

- Semi-planar/planar for YUV420

- YUY2/planar for 422H/422V

- Planar for YUV444

- Interleave for RGBA

# 2.7.4 Video Image Compositor (VIC)

VIC implements various 2D image and video operations in a power-efficient manner. It handles various system UI scaling, blending, and rotation operations, video post-processing functions needed during video playback, and advanced de-noising functions used for camera capture.

- > High-quality Deinterlacing

- Inverse Teleciné

- > Temporal Noise Reduction

- New Bilateral Filter as spatial filter

- Improved TNR3 algorithm

- Scaling

- Color Conversion

- > Memory Format Conversion

- > Blend/Composite

- > 2D Bit BLIT operation

- > Rotation

- > Geometry transform processing

- Programmable nine-points controlled warp patch for distortion correction

- Real-time on-the-fly position generation from sparse warp map surface

- Pincushion/barrel/moustache distortion correction

- Distortion correction of 180- and 360-degree wide FOV lens

- Scene perspective orientation adjustment with IPT

- Full warp map capability

- Non-fixed Patch size with 4x4 regions

- External Mask bit map surface

#### 2.7.5 Audio Processing Engine (APE)

The Audio Processing Engine (APE) is a self-contained unit with dedicated audio clocking that enables Ultra Low Power (ULP) audio processing. Software based post processing effects enable the ability to implement custom audio algorithms.

#### Features:

- 96 KB Audio RAM

- Audio Hub (AHUB) I/O Modules

- 2xI2S/2xDSPK Audio Hub (AHUB) Internal Modules

- Sample Rate converter

- > Mixer

- > Audio Multiplexer

- Audio De-multiplexer

- Master Volume Controller

- Multi-Channel IN/OUT

- Digital Audio Mixer: 10-in/5-out

- Up to eight channels per stream

- Simultaneous Multi-streams

- Flexible stream routing

- Parametric equalizer: up to 12 bands

- Low latency sample rate conversion (SRC) and high-quality asynchronous sample rate conversion (ASRC)

#### High-Definition Audio (HDA) 2.7.6

#### Standard

Intel High-Definition Audio Specification Revision 1.0a

The Jetson Xavier NX implements an industry-standard High-Definition Audio (HDA) controller. This controller provides a multi-channel audio path to the HDMI interface. The HDA block also provides an HDA-compliant serial interface to an audio codec. Multiple input and output streams are supported.

#### Features:

Supports HDMI 2.0 and DP1.4

- > Support up to two audio streams for use with HDMI/DP

- > Supports striping of audio out across 1,2,4<sup>[a]</sup> SDO lines

- > Supports DVFS with maximum latency up to 208 µs for eight channels

- > Supports two internal audio codecs

- > Audio Format Support

- Uncompressed Audio (LPCM): 16/20/24 bits at 32/44.1/48/88.2/96/176.4/192<sup>[b]</sup> kHz

- Compressed Audio format: AC3, DTS5.1, MPEG1, MPEG2, MP3, DD+, MPEG2/4 AAC, TrueHD, DTS-HD

[a] Four SDO lines: cannot support one stream, 48 kHz, 16-bits, two channels; for this case, use a one or two SDO line configuration.

[b] DP protocol sample frequency limitation: cannot support >96 kHz; i.e., does not support 176.4 kHz and 196 kHz.

# 2.8 Interface Descriptions

The following sections outline the interfaces available on the Jetson Xavier NX module and details the module pins used to interact with and control each interface. See the *Jetson Xavier NX Product Design Guide* for complete functional descriptions, programming guidelines, and register listings for each of these blocks.

# 2.8.1 SD/eMMC

| Standard                                                                           | Notes                                  |

|------------------------------------------------------------------------------------|----------------------------------------|

| SD Specifications, Part A2, SD Host Controller Standard Specification, Version 4.1 |                                        |

| SD Specifications, Part 1, Physical Layer Specification, Version 4.2               |                                        |

| SD Specifications, Part 1, eSD (Embedded SD) Addendum, Version 2.10                |                                        |

| SD Specifications, Part E1, SDIO Specification Version, 4.1                        | Support for SD 4.0 Spec without UHS-II |

| JEDEC Standard, Embedded Multimedia Card (eMMC) Electrical Standard 5.1            | JESD84-B51                             |

The SecureDigital (SD)/Embedded MultiMediaCard (eMMC) controller is capable of interfacing to an external SD card or SDIO device and provides the interface for the on-module eMMC. It has a direct memory controller interface and is capable of initiating data transfers between system memory and an external card or device. It also has an AMBA Peripheral Bus (APB) slave interface to access its configuration registers. To access the on-system RAM for MicroBoot, the SD/MMC controller relies on the path to System RAM in the memory controller.

- > 8-bit data interface to on-module eMMC

- > 4-bit data interface for SD cards/SDIO

- > Supports card interrupts for SD cards (4-bit SD modes) and SDIO devices

- Supports read wait control and suspend/resume operation for SD cards

- > Supports FIFO overrun and underrun condition by stopping SD clock

- > Supports addressing larger capacity SD 3.0 or SD-XC cards up to 2 TB

Table 2-9: SD/SDIO Pin Descriptions

| Pin# | Signal Name | Description             | Direction | Pin Type         |

|------|-------------|-------------------------|-----------|------------------|

| 229  | SDMMC_CLK   | SD Card or SDIO Clock   | Output    | CMOS - 1.8V/3.3V |

| 227  | SDMMC_CMD   | SD Card or SDIO Command | Bidir     | CMOS - 1.8V/3.3V |

| 219  | SDMMC_DATO  | SD Card or SDIO Data 0  | Bidir     | CMOS - 1.8V/3.3V |

| 221  | SDMMC_DAT1  | SD Card or SDIO Data 1  | Bidir     | CMOS - 1.8V/3.3V |

| 223  | SDMMC_DAT2  | SD Card or SDIO Data 2  | Bidir     | CMOS - 1.8V/3.3V |

| 225  | SDMMC_DAT3  | SD Card or SDIO Data 3  | Bidir     | CMOS - 1.8V/3.3V |

## 2.8.2 Universal Serial Bus (USB)

| Standard                                                                               | Notes                                                                                                                                      |

|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Universal Serial Bus Specification Revision 3.1                                        | Host mode only                                                                                                                             |

| Universal Serial Bus Specification Revision 3.0                                        | Device mode only                                                                                                                           |

| Universal Serial Bus Specification Revision 2.0                                        | USB Battery Charging Specification, version 1.2; including Data Contact Detect protocol Modes: Host and Device Speeds: Low, Full, and High |

| Enhanced Host Controller Interface Specification for Universal Serial Bus revision 1.0 |                                                                                                                                            |

An xHCI/Device controller (named XUSB) supports the xHCI programming model for scheduling transactions and interface managements as a host that natively supports USB 3.1, USB 2.0, and USB 1.1 transactions with its USB 3.1 and USB 2.0 interfaces. The XUSB controller supports USB 2.0 L1 and L2 (suspend) link power management and USB 3.1 U1, U2, and U3 (suspend) link power managements. The XUSB controller supports remote wakeup, wake on connect, wake on disconnect, and wake on overcurrent in all power states, including sleep mode.

## USB 2.0 Operation

Each USB 2.0 port (3x) operates in USB 2.0 high-speed mode when connecting directly to a USB 2.0 peripheral and operates in USB 1.1 full- and low-speed modes when connecting directly to a USB 1.1 peripheral. When operating in High-Speed mode, each USB 2.0 port is allocated with one High-Speed unit bandwidth. Approximately a 480 Mb/s bandwidth is allocated to each USB 2.0 port. All USB 2.0 ports operating in full- or low-speed modes share one full- and low-speed bus instance, which means 12 Mb/s theoretical bandwidth is distributed across these ports.

Table 2-10: USB 2.0 Pin Descriptions

| Pin# | Signal Name | Description          | Direction | Pin Type |

|------|-------------|----------------------|-----------|----------|

| 109  | USB0_D_N    | USB 2.0 Port 0 Data- | Bidir     | USB PHY  |

| 111  | USB0_D_P    | USB 2.0 Port 0 Data+ | Bidir     | USB PHY  |

| 115  | USB1_D_N    | USB 2.0 Port 1 Data- | Bidir     | USB PHY  |

| 117  | USB1_D_P    | USB 2.0 Port 1 Data+ | Bidir     | USB PHY  |

| 121  | USB2_D_N    | USB 2.0 Port 2 Data- | Bidir     | USB PHY  |

| 123  | USB2_D_P    | USB 2.0 Port 2 Data+ | Bidir     | USB PHY  |

## **USB 3.1 Operation**

The USB 3.1 port supports:

- > Generation 1 SuperSpeed USB (5 Gbps transfer rates)

- Generation 2 SuperSpeed USB (10 Gbps transfer rates)

Table 2-11: USB 3.1 Pin Descriptions

| Pin# | Signal Name | Description                        | Direction | Pin Type                                |

|------|-------------|------------------------------------|-----------|-----------------------------------------|

| 161  | USBSS_RX_N  | USB SS Receive- (USB 3.1 Ctrl #0)  | Input     | USB SS PHY, AC-Coupled (off the module) |

| 163  | USBSS_RX_P  | USB SS Receive+ (USB 3.1 Ctrl #0)  | Input     | USB SS PHY, AC-Coupled (off the module) |

| 166  | USBSS_TX_N  | USB SS Transmit- (USB 3.1 Ctrl #0) | Output    | USB SS PHY, AC-Coupled on carrier board |

| 168  | USBSS_TX_P  | USB SS Transmit+ (USB 3.1 Ctrl #0) | Output    | USB SS PHY, AC-Coupled on carrier board |

# 2.8.3 PCI Express (PCIe)

| Standard                                    | Notes                                                                                                                                                                                                                                                 |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCI Express Base Specification Revision 3.0 | Jetson Xavier NX meets the timing requirements for the Gen3 (8.0 GT/s) for x1 and Gen4 (16.0 GT/s) for x4 data rates. Refer to specification for complete interface timing details.  Although NVIDIA validates that the design complies with the PCIe |

|                                             | specification, PCle software support may be limited.                                                                                                                                                                                                  |

The Jetson Xavier NX module integrates two PCle controllers supporting:

- > Connections to two interfaces (1x1 + 1x4).

- > x1 (supports Root Port only), x4 (supports Root Port or Endpoint modes) Upstream and downstream AXI interfaces that serve as the control path from the Jetson Xavier NX to the external PCIe device

- > Gen3 (8 GT/s), supported on x1

- > Gen4 (16 GT/s) supported on x4

> Two PCIe controllers, five lanes for a total of 144 GT/s. One controller operates in x1 mode only. The second controller can operate in x1 or x2 or x4 mode.

Table 2-12: PCle Pin Descriptions

| Pin# | Signal Name | Description                               | Direction | Pin Type                                                               |

|------|-------------|-------------------------------------------|-----------|------------------------------------------------------------------------|

| 131  | PCIEO_RXO_N | PCIe #0 Receive 0- (PCIe Ctrl #5 Lane 0)  | Input     | PCIe PHY, AC-Coupled for<br>PCIe on carrier board if<br>direct connect |

| 133  | PCIEO_RXO_P | PCIe #0 Receive 0+ (PCIe Ctrl #5 Lane 0)  | Input     | PCIe PHY, AC-Coupled for<br>PCIe on carrier board if<br>direct connect |

| 137  | PCIEO_RX1_N | PCIe #0 Receive 1- (PCIe Ctrl #5 Lane 1)  | Input     | PCIe PHY, AC-Coupled for<br>PCIe on carrier board if<br>direct connect |

| 139  | PCIEO_RX1_P | PCIe #0 Receive 1+ (PCIe Ctrl #5 Lane 1)  | Input     | PCIe PHY, AC-Coupled for<br>PCIe on carrier board if<br>direct connect |

| 149  | PCIEO_RX2_N | PCIe #0 Receive 2- (PCIe Ctrl #5 Lane 2)  | Input     | PCIe PHY, AC-Coupled for<br>PCIe on carrier board if<br>direct connect |

| 151  | PCIEO_RX2_P | PCIe #0 Receive 2+ (PCIe Ctrl #5 Lane 2)  | Input     | PCIe PHY, AC-Coupled for<br>PCIe on carrier board if<br>direct connect |

| 155  | PCIEO_RX3_N | PCIe #0 Receive 3- (PCIe Ctrl #5 Lane 3)  | Input     | PCIe PHY, AC-Coupled for<br>PCIe on carrier board if<br>direct connect |

| 157  | PCIEO_RX3_P | PCIe #0 Receive 3+ (PCIe Ctrl #5 Lane 3)  | Input     | PCIe PHY, AC-Coupled for<br>PCIe on carrier board if<br>direct connect |

| 134  | PCIEO_TXO_N | PCIe #0 Transmit 0- (PCIe Ctrl #5 Lane 0) | Output    | PCIe PHY, AC-Coupled on carrier board                                  |

| 136  | PCIEO_TXO_P | PCIe #0 Transmit 0+ (PCIe Ctrl #5 Lane 0) | Output    | PCIe PHY, AC-Coupled on carrier board                                  |

| 140  | PCIEO_TX1_N | PCIe #0 Transmit 1- PCIe Ctrl #5 Lane 1)  | Output    | PCIe PHY, AC-Coupled on carrier board                                  |

| 142  | PCIEO_TX1_P | PCIe #0 Transmit 1+ (PCIe Ctrl #5 Lane 1) | Output    | PCIe PHY, AC-Coupled on carrier board                                  |

| 148  | PCIEO_TX2_N | PCIe #0 Transmit 2- (PCIe Ctrl #5 Lane 2) | Output    | PCIe PHY, AC-Coupled on carrier board                                  |

| 150  | PCIEO_TX2_P | PCIe #0 Transmit 2+ (PCIe Ctrl #5 Lane 2) | Output    | PCIe PHY, AC-Coupled on carrier board                                  |

| 154  | PCIEO_TX3_N | PCIe #0 Transmit 3- (PCIe Ctrl #5 Lane 3) | Output    | PCIe PHY, AC-Coupled on carrier board                                  |

| 156  | PCIEO_TX3_P | PCIe #0 Transmit 3+ (PCIe Ctrl #5Lane 3)  | Output    | PCIe PHY, AC-Coupled on carrier board                                  |

| Pin# | Signal Name   | Description                                                                      | Direction | Pin Type                                                 |

|------|---------------|----------------------------------------------------------------------------------|-----------|----------------------------------------------------------|

| 181  | PCIEO_RST*    | PCIe #0 Reset (PCIe Ctrl #5). $4.7k\Omega$ pull-up to 3.3V on the module.        | Bidir     | Open Drain 3.3V, Pull-up on the module                   |

| 180  | PCIEO_CLKREQ* | PCIe #0 Clock Request (PCIe Ctrl #5).<br>47kΩ pull-up to 3.3V on the module.     | Bidir     | Open Drain 3.3V, Pull-up on the module                   |

| 160  | PCIEO_CLK_N   | PCIe #0 Reference Clock–<br>Mux controlled by GPIO                               | Bidir     | PCIe PHY                                                 |